# Design Considerations for RS232 Interfaces

Design Note 27

Sean Gold

# Introduction

When designing an RS232 interface, it is necessary to conform to standards published by the Electronics Industry Association, EIA RS232.V28. Some key specifications are summarized in Table 1. However, the EIA specifications are often just the beginning of the design. Practical problems such as generating RS232 signal levels, providing sufficient load drive, and ensuring protection against fault conditions must also be considered.

Table 1. Key RS232 Transceiver Specifications (EIA RS232C.V28)

| SPECIFICATIONS    | VALUE                         | UNITS |

|-------------------|-------------------------------|-------|

| Signal Levels     | ±15 Max; ±5 Min               | V     |

| Cable Length      | 50 Max                        | Ft    |

| Load Capacitance  | 2500 Max                      | pF    |

| Cable Termination | 3k < R < 7k                   | Ω     |

| Data Rate         | 20k Max                       | Baud  |

| Slew Rate         | 3 < SR < 30                   | V/µs  |

| Fault Conditions  | Drivers Must Tolerate:        |       |

|                   | Conductor to Conductor Shorts | -     |

|                   | Line Open Circuit             | -     |

|                   | • ±25V Line Overage           | -     |

# **Power Supply Generators**

Creating the separate RS232 voltage levels is a common problem in systems which have only a 5V logic supply. Linear Technology has developed a family of transceivers that include an on-chip charge pump to generate the RS232 supplies. These transceivers are available in a wide variety of configurations incorporating up to 5 drivers and 5 receivers. Some transceivers have a SHUTDOWN control which turns off the charge pump and places the drivers in a "zero" power-high impedance state.

The charge pump consists of a relaxation oscillator, a capacitive voltage doubler, and a capacitive voltage inverter. The oscillator is designed to operate at a frequency well above the signal frequencies to avoid supply degradation as charge is rapidly removed from the storage capacitors. The LT®1180/LT1181's charge pump oscillator operates at approximately 200kHz, which is two times the frequency of the LT1080 and LT1130 series transceivers. The faster oscillator permits the use of low value capacitors ( $C > 0.1\mu$ F), and shortens the turn-on time from power off or SHUTDOWN state to less than 200µs. The LT1080 and LT1130 start up in approximately 2ms.

# Load Driving

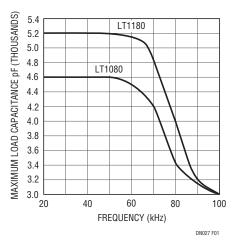

It is often desirable to exceed the 20kHz data rate or drive loads greater than 2500pF, e.g. long cables. Slew rate control in the drivers makes this objective possible without compromising the remaining specifications. When lightly loaded, the slew rate is set by an internal bias current and compensation capacitor. When heavily loaded, slew rate is limited by the output stage short circuit current and the load capacitance. The plot in Figure 1 shows the maximum load capacitance for a given data rate.

LT, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Figure 1. Max Load Capacitance vs Data Rate. Both Transceivers Use 1.0µF Storage Capacitors

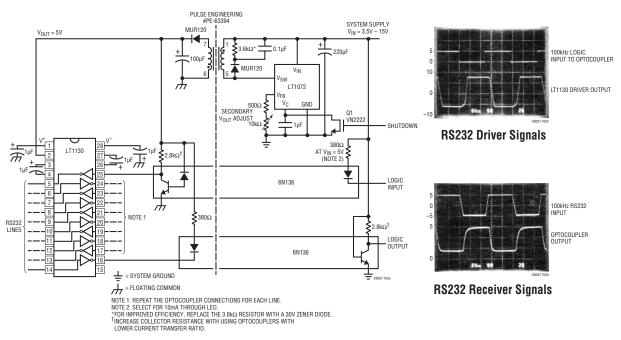

Figure 2. 2500V Isolated 5-Driver/5-Receiver RS232 Transceiver

#### **Fault Conditions**

In addition to protecting against all of the fault conditions described in Table 1, LTC transceivers are guaranteed for latchup free operation. When the drivers are turned off or SHUTDOWN, the output stage becomes high impedance; even when the output is pulled beyond the supply rails. The small current produced by overvoltage is not directed back into the supplies. High impedance on the driver outputs also eliminates signal feedthrough between the logic inputs and the RS232 lines.

When the device is turned on, overvoltage can, at most, pull the limited short circuit current from the supplies. The receivers are also short circuit current limited to prevent damage to unprotected logic circuitry.

#### **Isolated Transceiver**

The most frequent cause of failure in interface chips is exposure to extreme fault conditions. Protection against large differences in ground potential, high ground loop currents, or accidental high voltage connections mandates a fully isolated transceiver.

The circuit in Figure 2 provides 2500V isolation with optically coupled data lines and an isolated 5V supply. A powered transceiver eliminates the need for three supplies on both sides of the isolation transformer. High speed 6N136 optocouplers permit the LT1130 to operate at its full 100kHz bandwidth. However, slower, less expensive optoisolators, such as the 4N28, may be used when the data rate is less than 20k baud. The 5V power supply is generated with an isolated LT1072 switching regulator. The LT1072 has no electrical connection to the load; instead. the circuit derives its feedback from the transformers flvback voltage. This technique is often referred to as an isolated flyback regulator<sup>1</sup>. The regulator needs to deliver only modest current levels (200mA max), allowing a physically small isolation transformer. The circuit accepts 3.5V to 15V unregulated inputs which are readily available in most systems. Load regulation is 5% over a 200mA range of output current (50mA-250mA), and efficiency reaches 60% under maximum load conditions. Efficiency may be improved by 10% if the 3.6k $\Omega$  snubber resistor is replaced with a 30V Zener diode. Q1 provides shutdown control, which disables the interface to a low power state.

Note 1: Refer to Linear Technology's Application Note 19, pg. 30-34.

#### Data Sheet Download

www.linear.com/LT1180

For applications help, call (408) 432-1900

dn27f\_conv IM/GP 0889 165K • PRINTED IN THE USA

© LINEAR TECHNOLOGY CORPORATION 1989